Projects

BF SoC Hub co-innovation

SoC Hub co-innovation project, funded by Business Finland, started in 2020. Headed by Tampere University and Nokia, the SoC Hub co-innovation project consortium comprises CoreHW, VLSI Solution, TTTEch Flexibilis, Procemex, Wapice and Cargotec as partners.

SoC Hub co-innovation project, funded by Business Finland, started in 2020. Headed by Tampere University and Nokia, the SoC Hub co-innovation project consortium comprises CoreHW, VLSI Solution, TTTEch Flexibilis, Procemex, Wapice and Cargotec as partners.

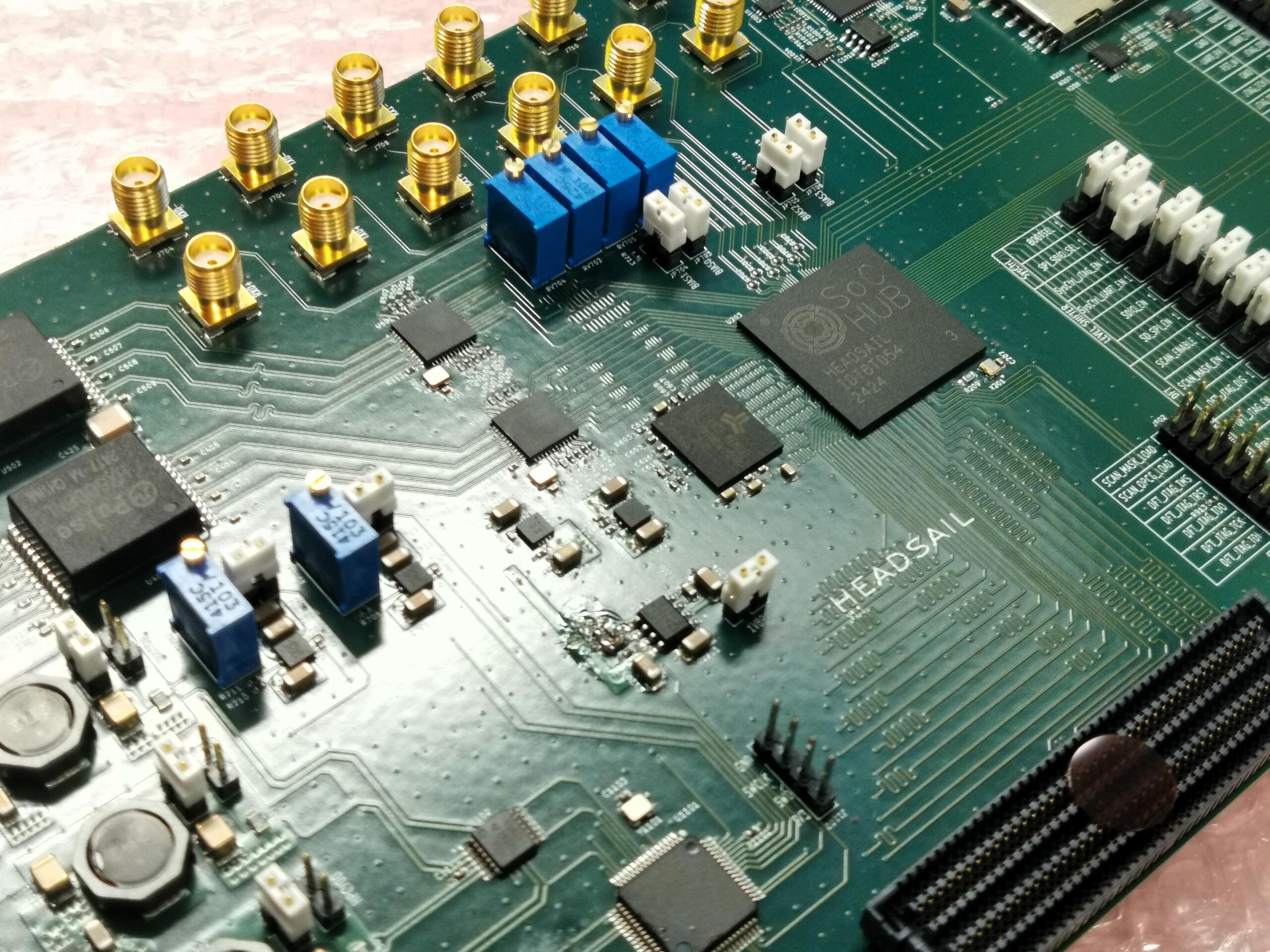

The consortium developed three System-on-Chips called Ballast, Tackle and Headsail. In the begininng, the chip development was started from scratch by setting up the necessary infrastructure, design flow and agreements as well as the chip template itself. The chips were designed all the way to tape-out, and sent to manufacture to TSMC.

The focus of the SoC Hub team was in rapid design flow time, and the leading idea of the project was to keep the pace of developing one chip per year. Read more here.

Edu4Chip

Education project Edu4Chip (Joint Education for Advanced  Chip Design in Europe) aims at enhancing chip design capability in Europe by designing and implementing study programmes that will increase the number of industry-ready chip design experts in Europe.

Chip Design in Europe) aims at enhancing chip design capability in Europe by designing and implementing study programmes that will increase the number of industry-ready chip design experts in Europe.

The main objective of Edu4Chip is to equip students with comprehensive knowledge and experience of the chip design process. To achieve this, a master’s study programme will be created, where the students will carry out a complete chip design, starting from the high-level description of the hardware and ending with the actual manufacturing (i.e., tape-out) and test of their chips.

The project includes nine European partners: Tampere University, Technical University of Munich, Technical University of Denmark, KTH Royal Institute of Technology, Institut Mines-Telecom and Fraunhofer, as well as SME partners MINRES Technologies, Logiq Works, and SyoSil Aps. The project is funded by the European Union in the Digital Europe Programme.

TRISTAN

European project TRISTAN started in December 2022 and will last until the end of 2025. Altogether in the consortium there are 46 partners from industry (both large industries as well as SMEs), research organizations, universities and RISC-V related industry associations from several different European countries. By joining the project, SoC Hub became a part of the most significant European RISC-V developer consortium. The main goal of the project is to develop and industrialize the European RISC-V ecosystem and increase its competitiveness.

European project TRISTAN started in December 2022 and will last until the end of 2025. Altogether in the consortium there are 46 partners from industry (both large industries as well as SMEs), research organizations, universities and RISC-V related industry associations from several different European countries. By joining the project, SoC Hub became a part of the most significant European RISC-V developer consortium. The main goal of the project is to develop and industrialize the European RISC-V ecosystem and increase its competitiveness.

TRISTAN aims at creating open source HW and SW components as well as open-source tools to boost European competence on chip designs. The focus is on RISC-V based System-on-Chips (SoC) that include cores and peripherals for the complete SoC architectures and accompanying software. The goals are very similar to the SoC Hub co-innovation project funded by Business Finland, and it brings the existing national activities to the European level. Together the projects build essential assets for commercially viable SoC designs. The aim is also to attract commercial interest by engaging potential application companies that currently use off-the-self chips in their products. The final goal of the project is to start new and affordable as well as differentiating commercial SoC projects based on the assets. The assets in the field of SoC design are intellectual property, networks and process knowledge.

Along with Tampere University there are three Finnish companies participating in TRISTAN: Nokia, VLSI Solution and Cargotec.

Open Application-Specific Instruction-set Processor (OpenASIP)

OpenASIP (formerly TTA-based Co-design Environment or TCE) is an open application-specific instruction-set toolset. It can be used to design and program customized processors based on the energy efficient Transport Triggered Architecture (TTA). The toolset provides a complete retargetable co-design flow from high-level language programs down to synthesizable processor RTL (VHDL and Verilog backends supported) and parallel program binaries. Processor customization points include the register files, function units, supported operations, and the interconnection network.

OpenASIP development is led by the Customized Parallel Computing (CPC) group at Tampere University.

DARE SGA1

The DARE project aims to advance European sovereignty in high-performance computing (HPC). The project designs and develops a general-purpose processor targeted to run major HPC workloads as well as two accelerators: A vector accelerator and an AI processing unit. On the hardware side, Tampere University’s Customized Parallel Computing (CPC) group is participating in DARE by researching coherent caches in the context of HPC. An efficient memory hierarchy is critical for the manycore processors used in HPC systems as providing data and enabling smooth synchronization can be become a bottleneck for performance. CPC also participates in developing a heterogeneous parallel computing software stack based on PoCL, ChipStar and SYCL with GROMACS as the optimized example HPC application.

PROFI7: System-on-Chip and Wireless Technology for Intelligent Machines

A multidisciplinary research group at Tampere University focusing on robotics, System-on-Chip (SoC), and wireless technology aims to make future working machines increasingly autonomous and safe, as well as energy and cost efficient. The Research Council of Finland has granted a total of EUR 3.5 million of profiling funding to the research area. The goal of the researchers is to create an autonomous heavy machinery solution consisting of new communication and sensor technology and similar advanced SoCs.

The profiling area System-on-Chip and Wireless Technology for Intelligent Machines consists of three large, independent research areas at the Faculties of Engineering and Natural Sciences and Information Technology and Communication Sciences at Tampere University. To create a truly intelligent, efficient, sustainable, and safe autonomous heavy machinery, it is essential to bring together the expertise on wireless communication, System-on-Chip, and robotics.